Write something

Decoupling capacitores Values

I have read in many CMOS IC datasheets that the typical values for decoupling capacitors are 100 nF, but on the other hand I have read an article by Eric Bogatin stating that this is a false myth and that this has been going on since the 80's when CMOS IC voltages were much lower. Actually he refers to calculate the decoupling capacitors with respect to the CMOS frequency and their rise times. Could someone clarify me which is the correct way of sizing the decoupling capacitors and the technical reasoning why? I would like to clear this doubt and when I search the internet I see disparity of opinions. thanks. Translated with DeepL.com (free version)

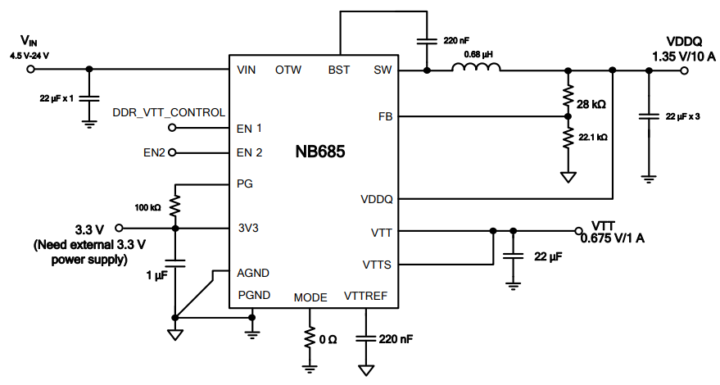

Why manufacturer sometimes use pariticular AGND and PGND for DC/DC?

Hi everyone, Sometimes I see separate AGND and PGND in DC/DC converters. But I don't understand how to connect them at the PCB level. I would appreciate it if you don't just tell me to check the manufacturer's documentation—I always do that. I just want to understand if everyone knows/understands the advantage of having separate AGND and PGND. And how to connect them at the PCB level? w/o AGND https://www.monolithicpower.com/en/documentview/productdocument/index/version/2/document_type/Datasheet/lang/en/sku/MPM3811GG-Z/?srsltid=AfmBOookF4rTW-Cev4suQY-0b8prv1BsC_usN-_Mg8VFNHBYDLx4vN_h w/ AGND https://www.monolithicpower.com/en/documentview/productdocument/index/version/2/document_type/Datasheet/lang/en/sku/NB685GQ/document_id/4378/

What would you like to learn more about?

Hi everybody! The field of PCB Design is vast, extremely vast! There are so many topics we could cover, but I would like to know more from you: What are the things you would like to learn more about? Write them in the comments section! P.S. Don't be shy about writing in the comments; let's make this a friendly community and a place we can all enjoy ;)

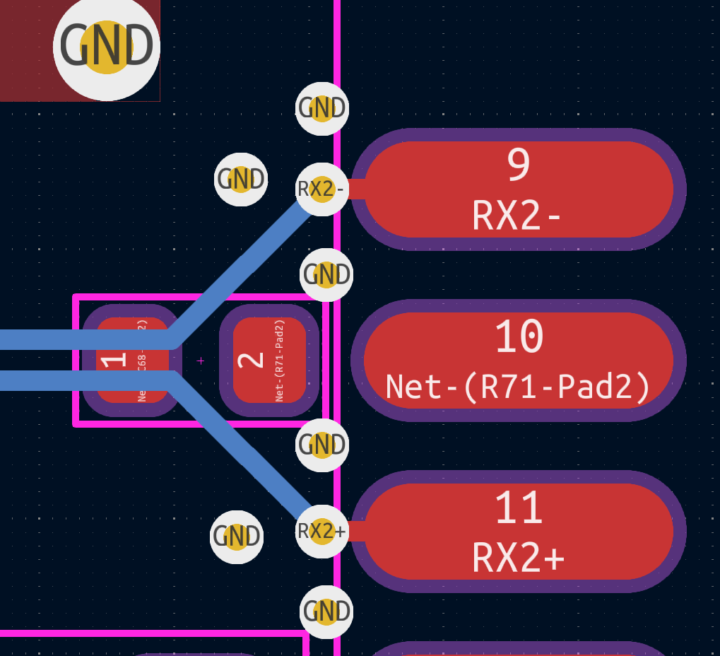

Referance vias for diff pairs (Ethernet)

Hi everyone, Maybe someone knows. Is it necessary to place return reference vias for differential pairs? in my case is Ethernet. Best regards, Nazar

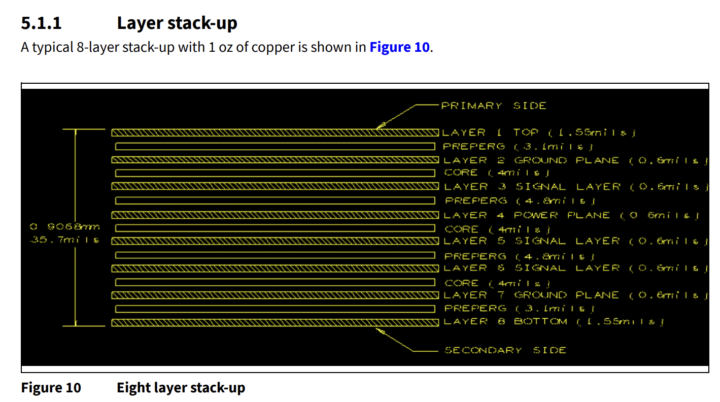

Is the layer stack-up from the manufacturer correct?

Dear community, I recently discovered a promising IC (USB HUB Controller, CCG6DF) for my project. However, I’ve noticed that the recommended layer stack-up provided may not be optimal. Please refer to the screenshot below for details. In your experience, should hardware designers strictly adhere to the datasheet recommendations, even if they seem less than ideal? Best Regards, Nazar Melnichek

1-13 of 13

powered by

skool.com/pcb-hackers-8346

Master professional electronic design and Printed Circuit Boards (PCB). Learn about EMC/EMI, signal & power integrity, high-speed design.

Suggested communities

Powered by